| Allicdata Part #: | 768-1258-ND |

| Manufacturer Part#: |

FT811Q-T |

| Price: | $ 0.00 |

| Product Category: | Integrated Circuits (ICs) |

| Manufacturer: | FTDI, Future Technology Devices International Ltd |

| Short Description: | IC GRAPHIC CTRL 48 PIN QFN |

| More Detail: | N/A |

| DataSheet: |  FT811Q-T Datasheet/PDF FT811Q-T Datasheet/PDF |

| Quantity: | 12089 |

| Series: | FT811Q |

| Packaging: | Tray |

| Part Status: | Active |

| Type: | Graphic Controller |

| Applications: | Video |

| Mounting Type: | Surface Mount |

| Package / Case: | 48-VFQFN Exposed Pad |

| Supplier Device Package: | 48-VQFN (7x7) |

| Base Part Number: | FT811Q |

Due to market price fluctuations,if you need to purchase or consult the price.You can contact us or emial to us: sales@allicdata.com

1. Feature

1. Advanced Embedded Video Engine (EVE) High-resolution graphics and video playback

2. FT81x features include graphic control, Audio control and touch control interface.

3. Pin assignment backward compatible with FT800 (FT810) and FT801 (FT811).

4. Support for multiple widgets to simplify design implement

5. Built-in graphical operations allow users to use Lack of expertise in creating high-quality displays

6. Supports 4-wire resistive touch screen (FT810/FT812)

7. Supports up to 5 capacitive touchscreens Touch Detection (FT811/FT813)

8. Hardware engine can recognize touch tags and Track touch movement. provide notice Up to 255 touch labels.

9. Enhanced sketch handling

10. Programmable interrupt controller provides Interrupt to Host MCU

11. Built-in 12MHz crystal with PLL Provides up to a programmable system clock 60MHz

12. Internal or external clock switching command clock source.

- External 12MHz crystal or clock Inputs are available for higher precision.

13. Video RGB parallel output; configurable as Supports PCLK and R/G/B outputs up to 60MHz 1 to 8 digits

14. Landscape and portrait support

15. Display enable control output to LCD panel

16. Integrated 1MByte graphics RAM, no frame Buffer RAM required

17. Supports playback of Motion JPEG encoded AVI video

18. Mono audio channel output with PWM output

19. Built-in speech synthesizer

20. PWM output for display backlight dimming control

21. Advanced object-oriented architecture support Low-cost MPU/MCU using SPI as system master interface

22. Supports single, dual or quad SPI data lines mode; SPI clock up to 30MHz

23. Power mode control allows the chip to be placed in Power-down, sleep and standby states

24. Supports I/O voltages from 1.8V to 3.3V

25. Internal regulator provides 1.2V to digital core

26. Built-in power-on reset circuit

27. -40°C to 85°C extended operating temperature scope

28. Available in compact lead-free VQFN-48 and VQFN-56 Package, RoHS Compliant

2. Application

1. Point-of-sale machines

2. Multifunction printer

3. Meter

4. Home security system

5. Graphical touchpad - remote control, dial pad

6. Remote/video conferencing systems

7. Telephone and switchboard

8. Medical Devices

9. Blood pressure display

10. Heart monitor

11. Blood sugar level display

12. Ventilator

13. Gas Chromatograph

14. Power meter

15. Electrical

16. STB

17. Thermostat

18. Display of sprinkler system

19. Medical Devices

20. GPS/Satellite Navigation

21. Vending machine control panel

22. Elevator control

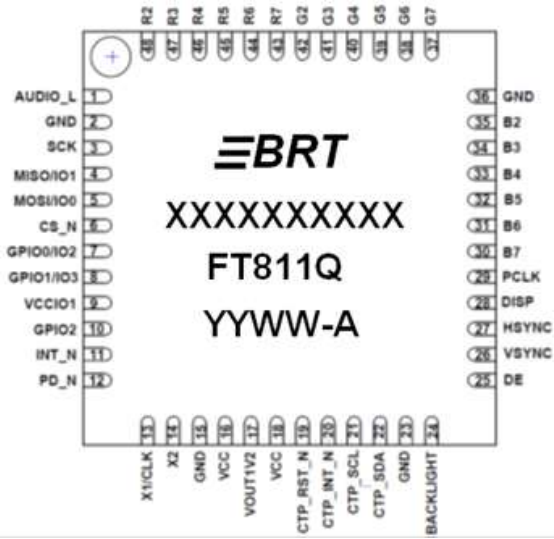

3. Pin configuration

4. Function Description

1. Quad SPI host interface

2. System clock

3. Graphics engine

4. Parallel RGB video interface

5. Audio engine

6. Touchscreen support and interface

7. Power management

5. QSPI interface

The QSPI slave interface operates at frequencies up to 30MHz. Only SPI mode 0 is supported. QSPI can be configured as SPI slave channel mode of SINGLE, DUAL or QUAD. By default, the SPI slave operates in single channel mode with MOSI as the input to the master and MISO as the output of the master. The DUAL and QUAD channel modes themselves are configurable via the SPI slave. To change the channel mode, write to register REG_SPI_WIDTH. In DUAL/QUAD channel mode, the SPI data port is now unidirectional. In these modes, each SPI The transaction will start from the data port set as input. Therefore, in order to write to the FT81x, the protocol will run as in the FT800 using "WR-Command/Addr2, Addr1,Addr0, DataX, DataY, DataZ... " The write operation is considered complete when CS_N becomes inactive high of. For reading from the FT81x, the protocol will still run as in the FT800, using "RD-Command/Addr2, Addr1, Addr0, Dummy Byte, DataX, DataY, DataZ ". However, since the data port is now unidirectional, a change is required The port direction change will occur before DataX is clocked out from the FT81x. Therefore, it is important that the firmware controlling the SPI master changes the SPI master data port direction to "input" after Send Addr0. The FT81x does not change port orientation until it starts outputting DataX. Therefore, neither the SPI master nor the slave is driving the bus; therefore, the datapath must have pull-ups/pull-downs.

6. Clock Frequency

By default the system clock is 60MHz when the input clock is 12MHz. The host is allowed to switch the system clock to other frequencies (48MHz, 36MHz, and 24MHz) by the host command “CLKSEL”. The clock switching command shall be sent in SLEEP mode only. When using the internal relaxation oscillator, its clock frequency is trimmed to be 12MHz at factory. Software is allowed to change the frequency to a lower value by programming the register REG_TRIM. Note that software shall not change the internal oscillator frequen Above 12MHz.

7. Internal Voltage Regulator and POR

An internal voltage regulator powers the core circuitry. It is recommended to use a 47kΩ resistor to pull the PD_N pin to VCCIO1, while using a 100nF capacitor to ground to delay the internal regulator from powering up after VCC and VCCIO are stable. The internal regulator requires a compensation capacitor for stabilization. A typical design requires a 4.7uF capacitor between the VOUT1V2 and GND pins. Do not connect any other load to the VOUT1V2 pin. When the output voltage is above the POR threshold. POR will reset all core digital circuits. The PD_N pin can be used as an asynchronous hardware reset input. Driving PD_N low for at least 5ms, then driving it high will reset the FT81x chip.

8. power mode

When powering VCCIO and VCC, the internal regulator is powered from VCC. Internal POR The pulses will be generated during the power-up of the regulator until it stabilizes. After the first power-on, The FT81x will remain in SLEEP state. When needed, the host can execute the SPI ACTIVE command by setting the FT81x to the ACTIVE state in the following ways. The graphics engine, audio engine, and touch engine only work in the ACTIVE state. To save power, the host can send commands to put the FT81x into any of the low power modes: STANDBY, SLEEP and POWERDOWN. Alternatively, the host can put the FT81x in POWERDOWN mode by driving the PD_N pin low, no matter what state it is currently in.

| Part Number | Manufacturer | Price | Quantity | Description |

|---|

| NHD-FT81X-SHIELD | Newhaven Dis... | 17.47 $ | 109 | ARDUINO SHIELD EVE2 TFT M... |

| FT813Q-T | FTDI, Future... | -- | 11989 | IC GRAPHIC CTRL 56 PIN QF... |

| FT810Q-T | FTDI, Future... | -- | 13107 | IC GRAPHIC CTRL 48 PIN QF... |

| FT811Q-T | FTDI, Future... | -- | 12089 | IC GRAPHIC CTRL 48 PIN QF... |

| FT812Q-T | FTDI, Future... | 5.12 $ | 1209 | IC GRAPHIC CTRL 56 PIN QF... |

IC HDMI TX 81MHZ 80-LQFP

IC VIDEO DECODER 4CH 80LQFP

IC VIDEO/AUDIO 8CHAN 128LQFP

IC MULTIMONITOR CTRLR 176TQFP

IC FILTER BUFFER VID 8-SOIC

IC VID/GRAPHIC DIGITIZR 100HTQFP