How to realize low power design in embedded system?

In embedded systems, low-power design is a problem that must be faced during product planning and design. Semiconductor chip performance doubles every 18 months. But at the same time, the battery technology cannot keep up with the pace of semiconductors. The capacity of batteries of the same size can be doubled in 10 years. The requirements for the use time and standby time of the embedded system are also getting higher and higher, which needs to fully consider the low power design of the entire system when designing the product. Power consumption control is a systematic project, which needs to be considered from the aspects of low-power device selection, hardware low-power design and manufacturing technology, and software low-power optimization. The author has summarized the key points of low-power design in embedded systems from the above perspectives on the projects served during the work of Runxin Technology.

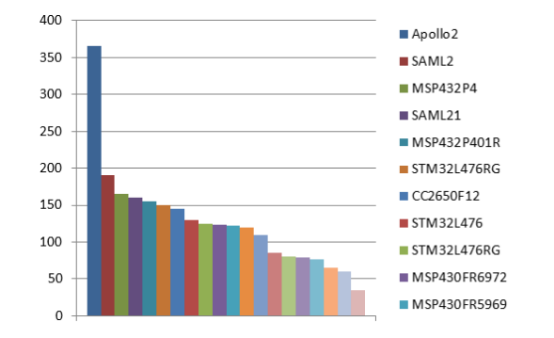

With the continuous development of semiconductor technology, the manufacturing process of semiconductors is also constantly improving. The use of advanced technology and low-power design components can reduce the power consumption of the entire system from the source. The selection of the main control chip must fully consider the use scenarios of the system. For those application scenarios with more computing tasks, you can use a chip with a high energy consumption ratio to design, such as the Apollo series chip like ambiq, which uses a patent With the SPOT technology, the chip operates steadily at sub-threshold, which can reduce energy consumption by nearly 13 times and realize the ultimate low power consumption technology.

For embedded systems, the power chip is an important device for low-power design. The power consumption and conversion efficiency of the power chip itself greatly affect the battery life. For the design of a low-power constant voltage circuit, low-power LDO or DCDC chips are required, such as TI's TPS797 series, and its own power consumption is only 1.2uA.

In the case of meeting the functional requirements, try to use external devices with trigger output function instead of external devices that need to be polled, which can reduce the running time of the MCU, usually the MCU can always be in sleep state, and there are external devices when the trigger conditions are met Wake up MCU work through interrupt. Hardware design is also a crucial factor for the power consumption of embedded systems.

For the power control of peripheral components, devices with a shutdown function are used. For peripherals that do not need to work in low-power mode, MOS tube circuits can be used with MCU control to perform power management on local circuits. When the device does not need to work, try to shut down the power supply to achieve lower power consumption.

Multi-level voltage design, voltage and power consumption are closely related. Therefore, the reduction of power consumption can be considered for different circuit modules, using different voltage levels, and DVFS dynamic voltage frequency technology can be used to reduce the system in real time by reducing the operating voltage and operating frequency of different circuit modules to just meet the minimum requirements of the system. The method of different circuit module power consumption. The hardware design must avoid IO port leakage current for each IO port of the MCU. When the peripheral is powered down, the IO port will still have potential power output, so the IO port needs to be configured to a low or high state by default to avoid leakage current.

Software optimization of power consumption involves multiple levels and aspects. Appropriately reducing the operating frequency of the CPU and the operating speed of the MCU can effectively reduce the current consumption during operation. The power consumption of the chip and the main frequency are linearly related. A higher clock frequency means a faster MCU operating speed. , Then the faster switching frequency of the CMOS circuit inside the MCU leads to higher operating current and standby current.

Use the MCU's standby mode reasonably, and put the MCU into a low-power sleep mode when no tasks need to be processed. For embedded products that use an embedded operating system, they generally enter sleep mode during idle tasks, but in order to further reduce power consumption and achieve an optimal design for low power consumption, we cannot directly put sleep or shutdown mode directly Idle tasks are sufficient. A more advanced sleep mechanism needs to be designed. For example, the TIckless low power consumption mechanism is used in the freertos operating system. After entering the idle task, first calculate the maximum time that can execute low power consumption, that is, find out How much time is left for the next high-priority task to be executed. Then the low power consumption wake-up time is set to this calculated time, after which the system will be woken up from the low power consumption mode and continue to perform multi-tasking.

Pay attention to the level status of each GPIO port, and configure all GPIO ports to high or low level before entering sleep to reduce leakage current. For external sensors and peripherals, it is also necessary to configure their power consumption mode before entering sleep to reduce the current consumption.

Reasonably close the internal modules of the MCU. For internal modules that do not need to work in Deep Sleep mode, turn off the clock and power to save power consumption. At the same time, focus on the analog IO port. The analog function is generally a large power consumer. In the AD / DA function Turn off as soon as possible when not in use, reducing the time to use the analog function. In addition, due to the need for non-stop refresh, the internal SRAM of the chip also consumes a certain current in sleep mode. Some SRAM can be configured to keep refresh in sleep mode to reduce power consumption.

For chips with wireless functions, configure reasonable standby parameters to reduce power consumption. For example, compared to the BLE chip CSR1010, in the BLE broadcast mode, the standby current at a broadcast interval of 60 ms is 394A. If the broadcast time is increased to 1.28S, the standby current is reduced to 28A. For wifi chips, such as the Qualcomm QCA4004 chip, the corresponding power consumption in the case of DTIM1 is 1.5mA, and in the case of DTIM10 it is reduced to 334A.

The low power consumption of embedded systems requires comprehensive consideration of various possible factors, conditions and states, careful consideration and analysis of various details, calculation and analysis of various possible solutions and methods, and best efforts to optimize The power consumption of the entire system achieves the purpose of saving the most energy.

If you want to know more, our website has product specifications for embedded system, you can go to ALLICDATA ELECTRONICS LIMITED to get more information