AMD single-bridge A55 and A75 chipset motherboard timing.

AMD single bridge A55, A75 chipset motherboard, can support AMD production of FMI and FM2 CPU, and CPU integrated graphics card. This section analyzes the working time sequence of AMD single-bridge motherboard by using microstar MSI-7697 which supports FMI_CPU.

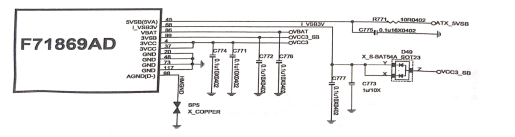

1. Plug in ATX power, and the purple line output VCC5_SB provides 5V power to IO chip, as shown in figure 1.

Figure 1 VCC5_ SB powers the IO chip.

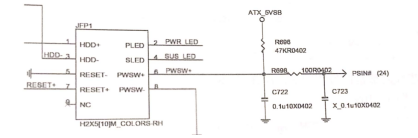

2. The short connector switch pin generates the PWSW+ trigger signal of 5v-0v-5v hopping (see figure 2), which is renamed as PSIN after resistance R698 and sent to 76 pin of IO chip.

FIG. 2 switch pin arrangement.

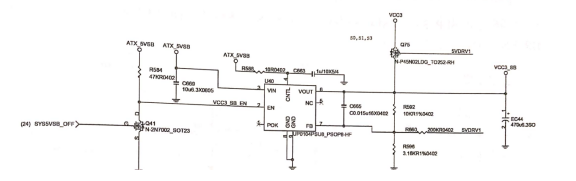

3. The IO chip sends SYSSVSB_OFF low level signal from pin 43, which is converted into VCC3_SB_EN by Q41, and sent to pin EN of U40 to start the chip operation, and outputs VCC3_SB standby power supply from pin 6, as shown in figure 3.

FIG. 3 VCC3_SB generating circuit.

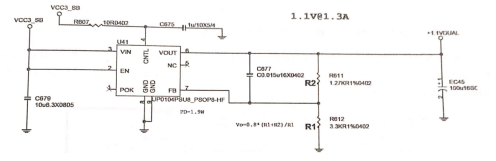

4. Vcc3_SB provides standby power supply to the bridge and IO chips, and sends it to the 3-pin and 2-pin of U41 chips, making the chip output +1.1VDUAL voltage, and provides the standby power supply of 1.1v to the bridge, as shown in figure 4.

Figure 4 +1.1VDUAL voltage generating circuit.

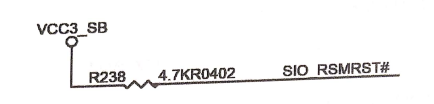

5.IO after VCC3_SB power supply is obtained by the chip, SI0_RSMRST signal is output through leakage, and the resistance R238 is pulled up to 3.3v high level to the bridge, indicating normal standby power supply, as shown in figure 5.

Figure 5 SIO_RSMRST# pull-up.

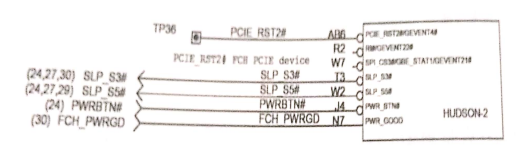

6.IO the internal delay of the chip sends a 3.3 v-0v-3.3 V hopping PWRBTN# signal to the PWR BIN# pin of the bridge to request power supply, as shown in figure 6.

FIG. 6 pin position of bridge trigger signal.

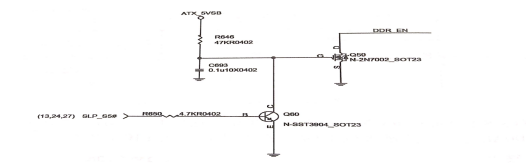

7. The bridge sends SLP_S5# and SLP_S3# sustained high level SLP_S5# through the circuit shown in figure 7 and converts it into DDR_ EN signal to start memory power supply.

FIG. 7 DDR_ EN conversion circuit.

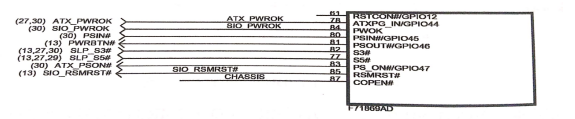

8. SLP_S3# signal is sent to pin 82 of IO chips. After IO chip conversion, ATX PSON# signal with a continuous low level of 0V is output from pin 83, as shown in figure 8. ATX PSON gives ATX power interface 16 pin, pull down the power green line to make the power output +12V, +5V, + 3.3v main power supply.

Figure 8 IO chip trigger pin.

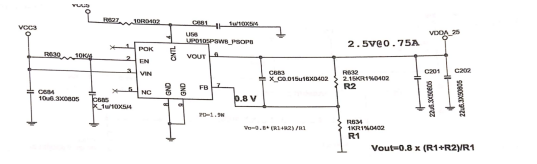

9. The power output VCC5 supplies power to U56, and the output Vcc3 supplies power to the chip's starting pin, making the chip work and output VDDA_25 to the CPU from the 6-pin, as shown in figure 9.

FIG. 9 VDDA_25 voltage generating circuit.

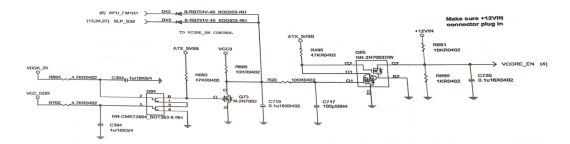

IO. VDDA_25,VCC DDR. SLP_S3#. APU_FMIRI generates high level VCOE_EN signal through the circuit shown in figure IO, starts the power management chip, and generates CPU core controller power supply VCC_NB.

FIG. IO VCORE_EN generating circuit.

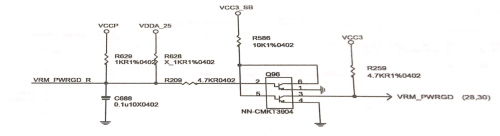

11. After VCORE and VCC_NB power supply is normal, the power management chip outputs VRM PWRGD R high level, which is converted into VRM_PWRGD signal through the circuit shown in figure 11, which is used to start VCCI 2REF power supply.

FIG. 11 VRM PWRGD signal conversion circuit.

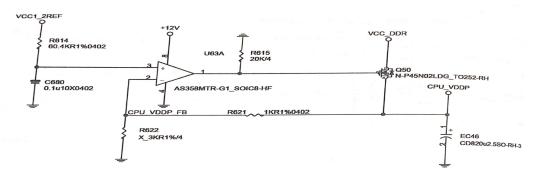

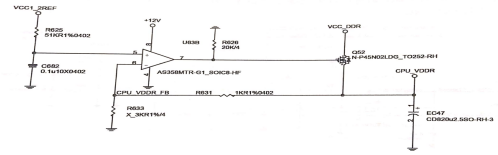

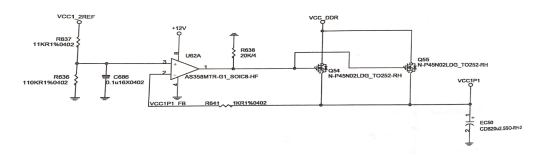

12. Power supply of VCC1_2REF generates CPU VDDP, CPU_VDDR and VCC1P1 through the control circuit, as shown in figure 12-14.

FIG. 12 CPU VDDP generating circuit.

FIG. 13 CPU VDDR generating circuit.

FIG. 14 VCC1P1 generating circuit.

13.ATX power supply delay sends 5V high level ATX PWROK signal from 8 pins, and sends it to 78 pins of IO chip to indicate that the power supply voltage is normal, and outputs 3.3v high level SIO PWROK signal from 84 pins after internal conversion of IO chips (see figure 8).

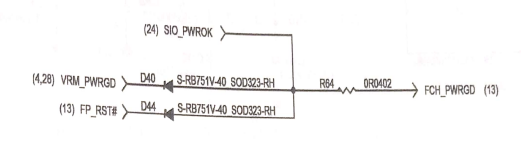

14. When SIO_PWROK is in contact with VRM PWRGD and FP RST#, a high level PCH PWRGD signal is generated for the bridge, indicating that the power supply of the main bridge is normal, as shown in FIG. 15.

FIG. 15 FCH PWRGD generating circuit.

15. The bridge sends high level signal of APU_PWRGD. One way to APU indicates normal power supply, and the other way to 35 pin of power management chip ISL6328 via resistance R464 renamed VRM PWROK.

FIG. 16 VRM_PWROK conversion circuit.

16. Bridge sends A RST# signal reset IO chip, PCIE RST# signal reset PCLE slot and network card chip, and PCIRST SLOT# signal reset PCI slot.

17. The bridge sends an APU RST# signal to reset the APU, and the APU starts to work.

If you want to know more, our website has product specifications for AMD single-bridge A55 and A75 chipset motherboard, you can go to ALLICDATA ELECTRONICS LIMITED to get more information