What are the benefits of using an FPGA with an on-chip high-speed network?

Reduce logic footprint and improve overall FPGA performance

Compared with the previous traditional FPGA, Speedster7t NoC has greater flexibility and a simpler design method. A potential benefit is that NoC will automatically reduce the amount of logic required for a given design. Designs can use NoC instead of FPGA logic arrays to route between modules. ACE design tools automatically manage the complexity of connecting design units to Speedster7t NoC, so designers do not need to write HDL code to achieve productivity. This approach simplifies the time-consuming challenge of achieving timing closure without reducing overall application performance due to routing congestion within the FPGA logic array. NoC can also improve device utilization without sacrificing FPGA performance, and can significantly increase the number of look-up tables (LUTs) available for calculation.

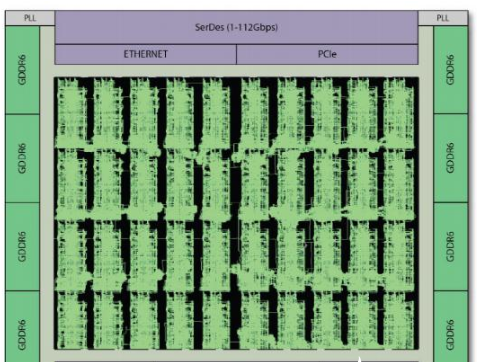

To emphasize this advantage, we have created an example design that supports convolution of two-dimensional input images. Each module uses Speedster7t machine learning processor (MLP) and BRAM module, each MLP performs 12 int8 multiplications in one cycle. Link 40 two-dimensional convolution modules together to utilize almost all available BRAM and MLP resources in the device. There are a total of 40 two-dimensional convolution example design examples running in parallel, using 94% MLP, 97% BRAM, but only using 8% LUT. Of the total available LUTs, the remaining 92% of LUTs can still be used for other functions.

As more examples are built into the device, the maximum frequency (FMAX) of a single unit module will not decrease. The design maintains performance because data entering and leaving each two-dimensional convolution module can directly access GDDR6 memory from the NAP connected to the NoC without routing through the FPGA logic array.

Figure 1: A Speedster7t device with 40 examples of 2D convolution modules in conclusion

Speedster7t NoC has achieved a fundamental transformation in the FPGA design process. Achronix is the first FPGA company to implement a two-dimensional network on chip (2D NoC), which can connect all system interfaces and FPGA logic arrays. This new architecture makes Achronix's FPGAs particularly suitable for high-bandwidth applications, while significantly improving designer productivity. Since NoC manages all network functions between the data accelerators and high-speed data interfaces designed in FPGAs, designers only need to design their data accelerators and connect them to the NAP primitives. ACE and NoC are responsible for all other matters. By using NoC, FPGA designers will benefit from:

1. Simplify high-speed data distribution throughout the FPGA logic array

2. Automatically connect PCIe interface to memory

3. Realize safe local reconfiguration on independent FPGA logic array module

4. Easily support hardware virtualization

5. Simplify team design

6. Accelerate design speed through independent interface and logic verification

7. Simplify 400 Gbps Ethernet application in packet mode

8. Reduce logic footprint and improve overall FPGA performance

If you want to know more, our website has product specifications for FPGA, you can go to ALLICDATA ELECTRONICS LIMITED to get more information