What is the world's first programmable carbon nanotube chip?

Researchers at MIT and Analog Devices created the first fully programmable 16-bit carbon nanotube microprocessor. It is by far the most complex integration of carbon nanotube-based CMOS logic, with more than 14,000 transistors, based on the RISC-V architecture, performing the same tasks as commercial microprocessors.

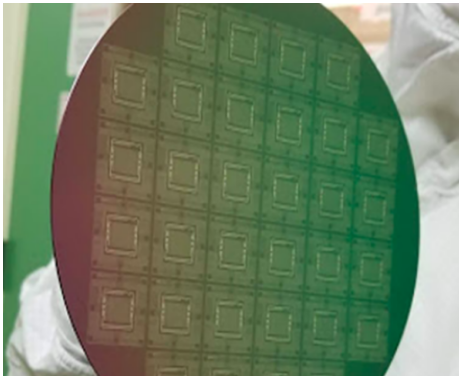

In the test, it also executed the classic "Hello World program": the chip is called RV16X-NANO, more than 70 pages of production process details are published in "Nature".

This is the most advanced chip made to date by emerging nanotechnology and is expected to be used for high performance and energy efficient computing. The researchers believe that the chip is designed and manufactured using industry standards, indicating a promising direction for electronics beyond silicon. Researchers have begun to apply these manufacturing processes to silicon chip manufacturing, funded by the Defense Advanced Research Projects Agency (DARPA).

Engineers are quite interested in this solution, which can free up space for systems with better or smaller performance, but due to the high processing temperatures, this solution is difficult to achieve in silicon. The RV16X-NANO chip also has shortcomings. Its transistor channel length is about 1.5 microns, which is equivalent to the silicon processor Intel 80386 introduced in 1985. The 80386 operates at 16MHz, while the maximum frequency of carbon nanotube chips is only 1MHz. This difference is due to the capacitance of the electronic components and the transistor. The ability to carry current.

It has been shown that the channel length of carbon nanotubes can be reduced to 5 nm. The density of nanotubes in each channel was increased from 10 per micron to 500 per micron. For randomly distributed nanotube networks, there may be an upper limit to the density, but new deposition techniques can increase the current density of such networks to 1.7 mA/μm. Thereby the width of the source and drain is reduced, allowing the electrodes to charge and discharge faster. In recent years, carbon nanotubes have been highly anticipated by academics and industry, and it is expected to become a perfect substitute for silicon, creating a new storm for the chip design community.

The chips developed by the MIT team have solved these problems to some extent. The microprocessor was developed on the basis of the previous version. The previous version was designed six years ago and has only 178 carbon nanotubes that can execute 1 bit of data. At the time, researchers began to address three specific challenges in producing such devices: material issues, production issues, and functional issues. Carbon nanotubes need to be purified to 99.999999%, and current technical conditions are difficult to achieve.

MIT researchers have proposed a technique called DREAM (an acronym for "designing resiliency against metallic CNTs") that reduces the purity requirements of carbon nanotubes by about four orders of magnitude, or 10,000 times. That is to say, the chip can be fabricated with a purity of 99.99%, and the current technology can be realized. The method of placing nanotubes in a specific precise position has not been mastered so far, and researchers have often produced them separately. However, this process causes a large number of carbon nanotubes to randomly gather together, and some metal nanotubes are mixed therein.

In response to the chaotic problem, the researchers created an oversized silicon surface that would ensure the growth of carbon nanotubes in the metal gap. To remove aggregates, they invented a method called RINSE that removes grown carbon nanotubes by selective stripping. They pre-applied a reagent on the wafer to enhance the adhesion of the carbon nanotubes. After the carbon nanotubes were placed, the wafer was wrapped with a specific polymer and then invaded into a solvent to take the aggregate away. A single carbon nanotube remains attached to the wafer.

In this way, they can precisely limit the nanotubes to the positioning area. Compared to similar methods, this technique can reduce the particle density on the chip by a factor of 250.

In the pressure of Moore's Law to slow down, researchers have been exploring new possibilities for chip design and manufacturing. Among them, carbon nanotube field effect transistor (CNFET) is the first choice to replace silicon material, which is expected to bring a new revolution to chip design. Compared to silicon, CNFETs are easy to make multi-layers with dense 3D interconnects, which can increase energy efficiency by 10 times and perform better power consumption. The researchers found that metal carbon nanotubes have different effects on the different pairs of logic gates.

For example, a metal carbon nanotube in the A gate may break the connection between A and B, but several metal carbon nanotubes in the B gate may not affect any connection between A and B. Through simulation experiments, the researchers found that all different gate combinations are robust to any metal carbon nanotubes and not robust to any metal carbon nanotubes. Taking into account the sensitivity of certain logic operations to metal nanotubes, the MIT research team modified the open source RISC design tool, customized a chip design program, and automatically learned the combination that was least affected by metal carbon nanotubes.

At the time of chip design, the program only uses a robust combination, ignoring the fragile combination, so that there is no gate that is most sensitive to metal carbon nanotubes in the chip. The RV16X-NANO chip contains more than 14,000 transistors with a 100% yield of carbon nanotubes. The RISC-V architecture instruction set can handle 16-bit data and 32-bit instructions, accomplishing the same tasks as commercial microprocessors. However, CNFET still has a series of difficulties to be overcome. For example, in mass production, there are often many defects that affect performance.

Binary calculations require two transistors: P-type and N-type. P-type or N-type semiconductors are usually realized in silicon by doping a small amount of other elements, but the carbon nanotubes are small, and this doping substitution mode does not contribute to the carbon nanotubes. In response, MIT researchers have developed a technology called MIXED (metal surface engineering and electrostatic doping crossover) to precisely adjust and optimize the function of the transistor.

The researchers attached metal oxides to the transistors and used atomic layer deposition techniques to manipulate the exact composition of the layers to convert the nanotubes into P-type or N-type. MIXED is a low temperature process so transistors can be built on top of other circuit layers without damaging them. In fact, the transistors in the RV16X-NANO are built into one layer of interconnects that provide power to the transistors and another layer that connects transistors to logic gates and layers of larger systems.

In theory, the manufacturing speed and energy consumption of this material are far superior to silicon chips. In terms of applications, in addition to being used in common notebooks, mobile phones, and IoT devices, microprocessors may also explore newer applications, such as microchips that can be injected into the body, and nanomachines that kill cancer cells in the body.

At present, carbon nanotubes have many limitations in classification, processing, sorting, and contact. If, as Shuranker said, carbon nanotube chips will be listed in five years, it will definitely bring new innovations to the global semiconductor field.

If you want to know more, our website has product specifications for the programmable carbon nanotube chip, you can go to ALLICDATA ELECTRONICS LIMITED to get more information