What are the reasons and conditions for interrupting ISR?

Interrupted ISR is different from other user software programs and belongs to a special class of functions. The reasons are as follows:

1. The interrupted ISR must be a void-type parameterless transfer function--the invisible parameter has no return value;

2. Interrupt ISR running time must be as short as possible to ensure the real-time performance of peripheral interrupts;

3. Interrupt ISR is triggered by hardware peripherals, not other function calls, and its running timing has random uncertainty and hardware real-time

The following work needs to be done in the interrupted ISR:

1. Handling peripheral interrupt events, such as timing count, communication peripheral RX data reception or MCU data buffer filling;

2. Clear the peripheral interrupt flag that caused the interrupt request to ensure that the peripheral does not lose the next interrupt due to the interrupt ISR operation, and the CPU can process other tasks after the interrupt exits;

In order to ensure the real-time nature of the interrupt, the interrupted ISR program should be as short as possible, and the conditional wait statement or even the infinite loop statement should be placed in the interrupt ISR. It is recommended that users generally only put critical processing in the interrupted ISR, and other related general work is performed in the main program. Typical examples such as CAN data reception are placed in the CAN RX Interrupt ISR, and the main program is notified by the global variables to execute the relevant diagnostic protocol (such as UDS).

Interrupt priority and interrupt nesting

Interrupt priority refers to the sequence of the kernel CPU in response to hardware peripheral interrupts. When different hardware peripheral interrupts are generated, the high-priority peripherals whose interrupt ISR is first executed by the kernel;

Interrupt nesting means that the peripheral interrupts have different priorities. When the CPU responds to the low priority interrupt (that is, when the interrupt ISR is run), the CPU global interrupt is turned on. If a higher priority interrupt arrives, the CPU The ability to stop the current interrupt processing area in response to high priority interrupts ensures high-priority task peripherals respond to real-time conditions:

Summarize the necessary conditions for interrupt nesting:

1. Different peripheral interrupt sources must have different priorities

The interrupt priority of some MCUs is fixed and unconfigurable. For example, the S12G series MCU has a fixed peripheral interrupt priority, and the higher the interrupt vector address is, the higher the priority is. The interrupt priority of other MCUs can be flexibly configured. For example, the peripheral interrupt of the S12XE series MCU has 8 priority settings and the peripheral interrupt of the Qorivva MPC56xx series MCU has 16 priority levels. The default priority of all MCUs is the same, so interrupt nesting is required. The corresponding peripherals need to be configured with different priorities according to the importance of the peripheral tasks;

2. The CPU global interrupt must be turned on in the interrupt ISR

Almost all embedded MCUs turn off the CPU global interrupt when the interrupt is pushed, that is, the interrupt nesting is disabled by default. To enable interrupt nesting, the user must interrupt the ISR in a peripheral that can be nested. Manually turn on the global interrupt of the CPU.

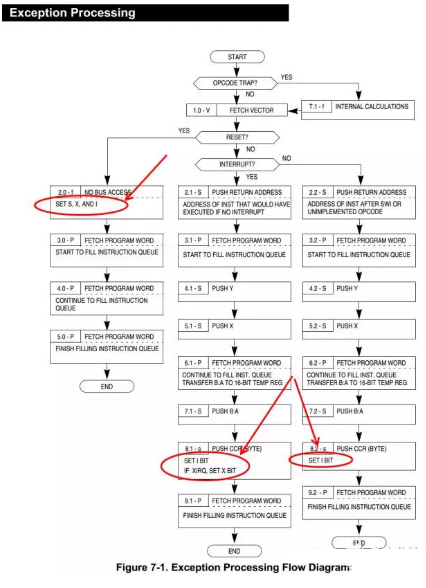

The following figure shows the S12 core CPU interrupt stack process, push the CCR register, turn off the global interrupt processing, the red circle in the arrow, the hardware sets I-BIT (disable I-bit peripheral interrupt), S-BIT (forbidden) STOP low power instruction) and X-BIT (XIRQ interrupt disabled) (Note: This process is an uncontrolled and uninterruptible "atomic" operation by the user)

The timing of turning on the global interrupt needs to be determined according to the specific task. It is generally recommended to open the interrupt ISR and clear the current peripheral interrupt flag.

Note that in some advanced MCUs, such as Qorivva MPC56xx and ARM Cortex M4F core-based first automotive-grade MCU--S32K series MCUs also integrate DMA, which can also respond to most of the on-chip peripheral interrupts, then, outside The interrupt flag is cleared by the DMA, and then the peripheral data is moved (without writing the peripheral interrupt ISR), thereby reducing the frequency of the CPU being interrupted by the peripheral and improving the CPU efficiency.

If you want to know more, our website has product specifications for interrupting ISR, you can go to ALLICDATA ELECTRONICS LIMITED to get more information