What is the extension method based on interface chip 8255?

Generally speaking, the programmable interface chip has a memory and an address line. The so-called programmable means that the CPU writes a certain data to a certain memory of the interface chip by using an instruction, and the interface chip automatically translates the data after receiving the data sent by the CPU. Then execute the action represented by the data

Different CPUs treat interface chips differently. Some CPUs treat the memory of the interface chip differently from the memory used by the CPU itself. The operation of the interface chip memory is called I/O operation, and the operation of the memory itself is used for the CPU itself. This is called memory operation, and I/O operations and memory operations use different instructions. This is called independent addressing of I/O ports.

The advantage of this method is that the I/O port does not occupy the address space of the memory, and the memory space and the I/O space are independent. The disadvantage is that the I/O port access instruction is separately set in the CPU, and the complexity of the CPU is increased. This structure is adopted by INTEL's 8086 series.

Another way of processing is to treat the memory of the interface chip as an external data memory without separately setting the access instruction of the I/O port. This method is called unified addressing, and the 8051 adopts this method.

Below we introduce the interface chip 8255.

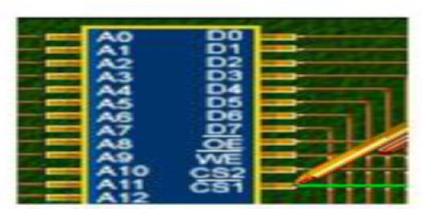

The 8255 is a parallel interface expansion chip. It has an 8-bit parallel interface D0-D7 to be expanded, and three extended 8-bit parallel interfaces PA, PB, PC. Four memories, PA port memory, PB port memory, PC port memory and control port memory are selected by its two address lines AO, A1.

When A1A0 is 00, 8255 connects D0-D7 to PA.

When A1A0 is 01, 8255 connects D0-D7 to PB.

When A1A0 is 10, 8255 connects D0-D7 to the PC.

When the A1A0 is 11, the 8255 connects the D0-D7 to the internal control register.

Suppose that two 8K data memories and a piece of 8255 are mixed and expanded into the external data memory of the CPU, and their chip select signals are connected in a decoding manner.

The input of the decoder 74139 is connected to P2.5 and P2.6 of the CPU.

When P2.6 and P2.5 are 00, the decoder output terminal YO is valid, and the first piece of data memory is selected. It can be seen that the logical addresses of the first slice memory are 0000H-1FFFH and 8000H-9FFFFH, and each physical unit has two logical address

When P2.6 and P2.5 are 01, the decoder output Y1 is valid, the second slice memory is selected, and the address of the second slice memory is 2000H-3FFFH and 0AOOOH-OBFFFH.

When P2.6 and P2.5 are 10, the decoder output Y2 is valid. When 8255 is selected, the logical address of 8255 is 4000H-5FFFH, and 0C000H-0DFFFH.

When P2.6 and P2.5 are 11, the decoder output Y3 is valid, and no memory is selected, that is, the address in this case is an invalid address, including 6000H-7FFFH, and 0E000H-OFFFFH.

If you want to know more, our website has product specifications for interface chip, you can go to ALLICDATA ELECTRONICS LIMITED to get more information