Do you know the knowledge of D triggers?

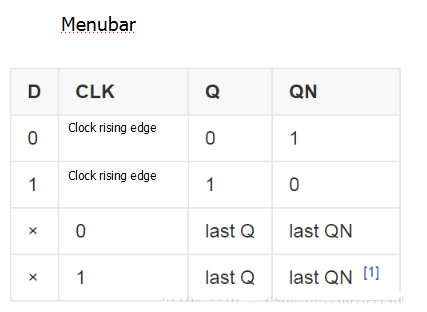

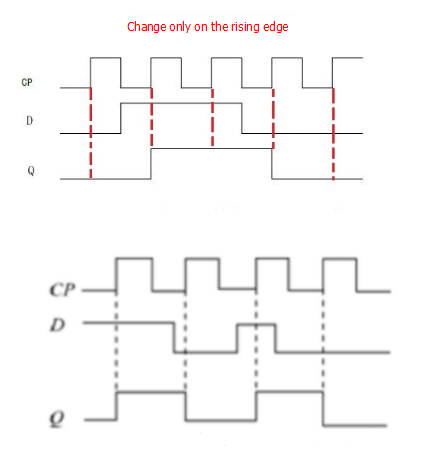

The D flip-flop is a memory storage device with two stable states. The flip-flop has two stable states, namely “0” and “1”, which can be flipped from a stable state to the external signal. Another steady state. Here will introduce the edge-triggered D flip-flop is triggered. The D flip-flop flips on the leading edge of the clock pulse CP (positive transition 0→1), the secondary state of the flip-flop (the next state) depends on the state of the D-end before the rising edge of the pulse of the CP, that is, the secondary state Q=D. Therefore, it has two functions of setting 0 and setting 1. Since the circuit has the function of maintaining blocking during CP=1 (ie, the output of the flip-flop is unchanged), during the CP=1, the data state of the D terminal changes, and the output state of the flip-flop is not affected, so the edge D flip-flop is disturbed. The possibility is reduced.

Common circuits, as well as conventional logic gates, have one thing in common, that is, the output is directly dependent on the input, and when the input disappears, the output does not exist. The trigger is different, and when it fires, the output changes. However, when the input is undone, the output is still maintained.

That is to say, the trigger has the ability to remember. A few years later, when engineers wanted to save a bit on a computer, they thought of a trigger. However, the R-S trigger has two outputs, and saving one bit does not need to be so much.

The solution is to leave only one output Q, and Q 'discard is not used (cut its lead). In this way, the saved bit can be observed from the Q side, or it can be taken away and used elsewhere. Through it, you can know what the current trigger is saving, whether it is 0 or 1.