What is AgilexTM's core competitive advantage from Intel?

1, Intel 10 nanometer process

Intel has dominated the semiconductor industry for decades, relying on two unique technologies: the first is the well-known x86 architecture, and the second is the semiconductor manufacturing process that has been far ahead of the competition. This has also led to Intel's famous "TIck-Tock" strategy, where architecture and process updates are interleaved year by year while maintaining a steady increase in processor performance.

However, the chip giant encountered obstacles in the 10 nanometer process. In fact, Intel also predicted that 10 nanometers of research and development will take longer than before, but no one may have thought it would be so long.

As a result, in the past one or two years, competitors who have been left behind are completing overtaking at the craft node of 10 nanometers. TSMC and Samsung are gradually putting their own 10 nanometer processes into mass production.

Finally, Intel, which was painful at the beginning of 2019, released four chips based on 10 nanometer technology, covering multiple application areas such as personal computing platforms, data centers, and 5G networks, and will officially ship production as soon as the end of the year. The AgilexTM FPGA released this time is also the flagship FPGA product based on Intel's 10nm process.

For the chip process, Intel's process often has better performance under the same process node, which is also recognized in the industry. Once Intel's ten-nanometer process is stable and mass-produced, it is expected to bring 20%-30% performance and power consumption advantages over competitors.

2, system level 3D chip

Heterogeneous integration and packaging of system-level 3D chips is also one of Intel's unique cheats. There are two main technologies, one is EMIB (embedded multi-die interconnect bridge), which provides high-speed interconnects for multiple heterogeneous wafers; the other is the latest Foveros 3D package technology announced in 2019.

In AgilexTM FPGAs, second-generation EMIB technology is used to connect programmable logic arrays and the surrounding chiplets. Since EMIB does not require the introduction of an additional silicon interposer, a large number of through silicon vias are not required, which significantly reduces the manufacturing complexity of the system. At the same time, it is not necessary to use long wires in the interposer, thus reducing the transmission delay between different wafers and reducing signal transmission interference. In addition, it is easier to replace different chipset sets without having to redo the entire chip system.

3, CXL: the ultimate solution for interconnecting CPU and FPGA

Currently, a major application scenario for FPGAs is as a hardware accelerator for CPUs in the data center to accelerate various applications, such as deep learning model training, financial computing, and network function unloading.

In the CPU area of the data center, Intel's Xeon® CPU has always been the absolute strongest. As an FPGA for data center accelerators, the first thing to consider is compatibility with Xeon® CPUs. Obviously, as an AgilexTM FPGA with "pure blood", it has been a good time from the beginning of its birth.

Cache coherency has always been one of the core issues that need to be addressed in the field of hardware accelerators. The main way to solve this problem is to clarify and popularize the memory interconnection protocol between the CPU and the hardware accelerator, just like the well-known PCIe protocol for CPU and accelerator communication.

In March of this year, Intel announced that it would join forces with Microsoft, Ali, Cisco, Dell EMC, Facebook, Google, HP Enterprise HPE and Huawei to create a new interconnect standard called Compute Express Link – CXL.

Interestingly, CXL's sponsors have four Internet giants, two server device manufacturers, and two network device manufacturers. This multi-dimensional presentation presents the target application areas of CXL: Internet data centers, communication infrastructure, cloud computing and cloud services. These areas are also an important platform for FPGAs to show their talents.

For AgilexTM FPGAs, it will natively support the CXL protocol and will be the industry's first memory-consistent hardware accelerator for Xeon® scalable processors. It is worth noting that the CXL protocol is based on PCIe design and extension, as shown in the following figure, so that the PCIe PHY and channel can be fully multiplexed, which is significantly easier to use than other similar protocols.

Therefore, AgilexTM's native support for CXL is bound to bring a huge "human and" advantage to its widespread use in the data center on the basis of "time and time" and "land".

One of the biggest advantages of FPGAs in artificial intelligence applications is the ability to use variable-precision word-length representations and mathematical operations, resulting in tremendous performance gains. In existing Intel FPGAs, fixed point numbers for curing and DSP operations for FP32 are already supported.

In AgilexTM FPGA, the DSP operations of FP8, FP16 and BFLOAT16 are extended, and the number of 9x9 multipliers and the configuration of multipliers are also added. These innovations for AI applications will also greatly enhance the future use of FPGAs in the AI field.

5, enhanced version of the Hyperflex architecture

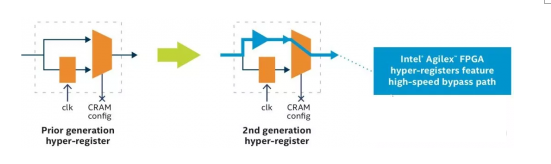

The main idea of Hyperflex is to add a lot of small registerscalled hyper-register on the routing network of the FPGA, so that the longer long timing path can be divided into multiple shorter paths to achieve the frequency boosting effect.

But in many cases, not all hyper-registers will be used. In order to reduce the extra delay, more requirements are placed on the retiming and automatic pipeline algorithms in the FPGA design tool.

In Intel's AgilexTM FPGAs, this problem has been specifically reinforced. The method is very simple and rude, which is to minimize the delay of the hyper-register bypass path (up to 40%), as shown below. Thus, when some hyper-registers are not used, the corresponding system delay can reach the wire level standard.

6, OneAPI: Intel's ambition

At Intel Architecture Day in late 2018, Intel's chip chief architect Raja Koduri announced a "big thing" that the company is working on: a software programming framework called OneAPI.

As its name suggests, OneAPI will provide a unified programming interface for Intel's CPU, GPU, FPGA, and hardware accelerators for various AI and other applications, allowing developers to switch and optimize between the underlying hardware at will. OneAPI's slogan is "The transistor can't be less", which is a good summary of OneAPI's ultimate goal.

In addition to the programming interface, OneAPI must also contain a complete development environment, libraries, drivers and other necessary elements, which represents Intel's greatest ambition, is to connect all of its chips and hardware products through this software system, and achieve Seamless switching. At the same time, it is foreseeable that Intel will gradually build an ecological environment around this software system. So once this system is implemented, it will be an advantage that no other competitor can match.

For the newly released AgilexTM FPGA, it will also be the first Intel FPGA product to support OneAPI.